(緑色)が3つ表示されればエラーなく合成完了.

(緑色)が3つ表示されればエラーなく合成完了.このドキュメントは http://icrus.org/fpga_atlys_design/ 上にあります.

本日はISEのインストールと『LEDチカチカ』を実行します.

これらは,前準備段階です.インストール及び接続が終了して,LEDチカチカプログラムを入力し,コンパイル→FPGAボードデータ転送を行い,LEDチカチカが動作した状態がスタートラインです.本日はスタートラインまでの準備体操といったところです.

以下を参考にして,各自でダウンロード・インストールを行って下さい

Xilinx社ダウンロードサイト

http://japan.xilinx.com/products/design-tools/ise-design-suite/ise-webpack.htm

(Xilinx社開発ソフトウェアISE WebPACK紹介ページ)

http://japan.xilinx.com/support/download/index.html/content/xilinx/ja/downloadNav/design-tools.html

から

Vendor 14.7 で

『 Windows 用フル インストーラー (TAR/GZIP - 6.18GB)』をダウンロードする.

登録IDでログオンする(id:t??y?? pw:h**4)

(ダウンロード時にログインを要求されますので各自でXilinxサイトにユーザ登録して下さい)

得られたファイルXilinx_ISE_DS_Win_14.7_1015_1.tar

解凍してディレクトリに展開しておく.

http://www.digilentinc.com/ より

左側のProductsから

Software→Adept 2 から(Adept 2 for Windows:)

Adept 2.16.1 System, 32/64-bit Windows

をダウンロードして得られたファイル

digilent.adept.system_v2.16.1.exe

64ビット版は条件により動かない場合があるので,今回は32ビット版をインストールします.

以下のディレクトリを辿って

Xilinx_ISE_DS_Win_14.7_1015_1\bin\nt

の下の

xsetup.exe

をダブルクリックで起動します.

ISE 14.7 Installer

Welcom [Next>]

Accept License Agreements (1 of 2)

□I accept and agree to the terms and conditions above

□I also aceept and agree to the following terms and conditions

にνマーク [Next>]

Accept License Agreements (2of 2)

□I accept and agree to the terms and conditions above

にνマーク [Next>]

Select Products to Install

Editon Listの下

○ ISE WebPACK

を選ぶ [Next>]

Select Installation Options

そのまま [Next>]

Select Destination Directory

そのまま [Next>]

Installation Options Summary

そのまま [Install]

インストールには,しばらく時間がかかる.(15分間?)

(コンピュータウィルスチェックソフトが動作していると時間がかかる)

次からの記述はOSやインストール履歴などによって途中で出現する場合がある

Microsoft Visual C++ 2008 Redistributalbe Setup

[Next>]

Licence Terms

□I have read and accept the license terms.

にνマーク [Install>]

Setup Complete

[Finish]

プログラム互換性アシスタント

WipPcap installer CACE technologies

→[ヘルプ情報を使用せずにプログラムを実行する(R)]

WipPcap 4.1.1 Setup

[Next>]

Welcom to the WinPcap 4.1.1 Setup Wizard

[Next>]

License Agreement

[I Agree]

Installation options

[Install]

Completing the WinPcap 4.1.1 Setup wizard

[Finish]

Xilinx Software Setup

Driver installation falled. Please check the Install

Directory/.xinstall/install.log file for more information on the cause of the installation failure.

[OK]

Cable Driver Installer

Please disconnect all Xillinx Platform cable USB or Evalution Platform

JTAG cables from this system before continuing.

[OK]

Windowsセキュリティ

このデバイスソフトウェアをインストールしますか?

名前:Jungo

発売元:Jungo LTD

□”Jungo LTD”からのソフトウェアを常に信頼する

のVをはずす.

[インストール]

Windowsセキュリティ

このデバイスソフトウェアをインストールしますか?

名前:Xilinx,Inc

発売元:Xilinx

□”Xilinx”からのソフトウェアを常に信頼する

のVをはずす.

[インストール]

場合によって出現するダイアログはここまで.

Xilinx License Configuration Manager

が起動する

○ Get Free Vivado/ISE WebPack liense/

を選び [Next]

ダイアログボックスが表示されるので [Connet Now]

ログインが継続している場合はユーザのプロパティが表示されるので [Next]

それ以外は登録したユーザIDとパスワードで再ログインする

Certificate Based Licenses で

□ ISE WebPACK License

をVチェックして

[Generate Node-Locked License]をクリック

ダイアログが表示されるので

3COMMENTS に

自分のIDなどメモを入力して [Next]

4REVIEW LICENSE REQUEST を確認して [Next]

成功する登録したメールアドレスに、Xilinx.lic(ライセンスファイル)がメールに添付されて送られてくる

Web上での表示

Congratulations

Your new license file has been successfully generated and e-mailed to ???@m.dendai.ac.jp. You can also view the license file under the Manage Licenses tab.

Please add this sender (xilinx.notification@entitlenow.com) to your address book.

表示ダイアログ

License File DetailsNode License

Host ID: ANY

ProductsISE WebPACK License (No Charge): 1 seats

メールで送られてきたXilinx.licを

C:\Xilinx\14.7

の下にコピーする

Xilinx license Configuration Managerの

Acquire a Licenseタグから

○ Locate Existing License(s) を 選択し [Next]

[Load License...] をクリックしコピーしたXilinx.licを選ぶ

License installation was successful.が表示されたら [OK] クリック

ウィンドウ下方の[Refresh]をクリックし

Expiration Dateが変わったことを確認して [Close]

ISE 14.7 Installerを

[Finish] で終了する (まだ閉じていなかった場合)

ライセンスマネジャーが起動しなかったときや閉じたときは以下より起動できる

C:\ProgramData\Microsoft\Windows\Start Menu\Programs\Xilinx Design Tools\ISE Design Suite 14.7\Accessories

Windows7は スタート → すべてのプログラム → Xilinx Design Tools → ISE Design Suite 14.7 → Accessories → Manage Xilinx Licenses

ダウンロード済みのファイル digilent.adept.system_v2.16.1.exe をダブルクリック実行してインストール

ユーザーアカウント制御

次のプログラムにこのコンピュータへの変更を許可しますか?

[はい(Y)]

Digilent Adept Setup

Welcom

[Next>]

License Agreement

[I Agree]

Choose Components

そのままで

[Next>]

Shortcut options

□create Quck Launch shortcuts?

にνマーク

[Next>]

Choose Install Location

そのままで

[Install]

Installation Complete

[Next>]

Completing the Digilent Adept Setup Wizard

そのまま

[Finish]

説明PDFファイルが立ち上がるが終了しておく.

Digilent Adeptが立ち上がることを確認して,それを終了する.

以上でインストール完了.

デスクトップ上にISE Design suite 14.7のショートカットがない場合は

c:\Xilinx\14.7\ISE_DS\ISE\bin\nt

の下の

ise.exeのショートカットをデスクトップに作る.

←このショートカットを使って,Xilinx開発環境の"ISE"を立ち上げる

デスクトップ上にAdeptのショートカットがない場合は

c:\Program files(x86)\digilent\adept

の下の

Adept.exeのショートカットをデスクトップ上に作る.

←このショートカットを使って,回路データ転送用ソフト"Adept"を立ち上げる.

ISEはFPGA用の開発環境を提供します.基本的な部分は無料で利用できます.この環境でプログラミングを行い,デバッグしてFPGA用の回路データを作成します.作成した回路データはAdeptを使ってUSBケーブルを通してATLYSに転送します.転送が完了しますと自動的に回路が動作を始めます.インストールが完了したら早速,「LEDチカチカ」を動作させましょうか.

プログラムは簡単です.しかしこのプログラムにより結構複雑な回路がISE により自動的に生成されます.実際にFPGA上に作成される回路図を見ることも出来ます. ここで使うアプリケーションソフトは次の通りです

デスクトップ上のISE Design Suite 14.7をダブルクリック

New Project Wizardが立ち上がる

Name: test

(注意 Location:をc:\Users\***\Documents\verilogなどのように決めておくとプログラムを見失わない.)

[Next]

Project Settings

Family → Spartan6

Device → XC6SLX45

Package → CSG324

Preterred Language → Verilog

[Next]→[Finish]

Select source type : Verilog Module

Filename : test

[Next]→[Next]→[Finish]

test.vのひな形が作成される

Select Source type : Implementation Constraints File

File Name : test

[Next]→[Finish]

test.ucfのひな形が作成される

ISEのバグのために合成に失敗するのを防ぐために新しいプロジェクトを作成したときはこれを行う.

"//"以降の記述はコメント文なので入力は任意

先頭の4桁は行番号なので入力しないこと

これで回路の合成が始まる.

この作業には2分程度かかる.

(緑色)が3つ表示されればエラーなく合成完了.

(緑色)が3つ表示されればエラーなく合成完了.

test.bitファイルが出来上がる.

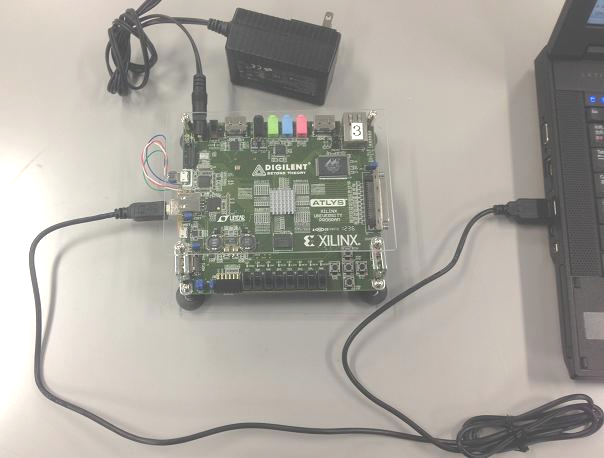

図1 Atlysの接続図

Adeptアイコンをダブルクリックする.

成功するとLD0が1秒間隔で点滅する.ここまでうまくいけば,ATLYSやISEの動作チェックは良好である.この回路はATLYSの内部クロック100MHz(1億Hz)を利用するので99,999,999カウントのタイミングで次のカウンタ値を0にセットすることにより1Hzの信号を得る.

*.vファイルはvelilogファイルですので論理をどんどん書いてください.それがそのままFPGA の振る舞いになります.

*.ucfファイルはFPGAチップ と外の世界との接点を指定しますので,どの端子利用するかによって指定が変わります.

000 `timescale 1ns / 1ps

001 ///////////////////////////////////////////////////////////////////////////////

002 // Create Date: 19:25:11 12/24/2012

003 // Module Name: test

004 ///////////////////////////////////////////////////////////////////////////////

005 module test(

006 input wire clk0,

007 output wire led

008 );

009

010 assign led=c[26];

011 reg[26:0] c=0;

012

013 always @( posedge clk0 )begin

014 if( c==27'd99999999 )

015 c <= 0;

016 else

017 c <= c + 1'b1;

018 end

019

020 endmodule

短いプログラムですが,重要な要素が含まれています.解説を読みながらよく理解してください.

000 NET "clk0" LOC = L15; // CLK

001 NET "led" LOC = U18; // LD0

ISEウィンドウ左側の (緑色)表示の一つ上,User Constraintsの下Floorplan Area/IO/Logic(PlanAhead)をダブルクリックし,しばらく(1分弱)待つとPlanAheadが起動する.Schematicタブをクリックすると実際に合成される回路図が表示できる.

(緑色)表示の一つ上,User Constraintsの下Floorplan Area/IO/Logic(PlanAhead)をダブルクリックし,しばらく(1分弱)待つとPlanAheadが起動する.Schematicタブをクリックすると実際に合成される回路図が表示できる.

ファイルをATLYS上のフラッシュROMに書き込むことで,ファイル転送なしでプログラムを起動できる.単独起動については後に示す.

atlysリファレンスマニュアル https://www.digilentinc.com/Data/Products/ATLYS/Atlys_rm_V2.pdf

VerilogHDL簡易文章書 http://icrus.org/machida/product/verilog.pdf

おつかれさまでした.以上,本日はLEDチカチカまででした.

来週はカウンタと7セグメントLED表示をします.

LEDチカチカが完成しないと次には進めませんので,このモジュールの完成を宿題としますので,解説も理解しながら実行しておいてください.

このドキュメントは http://icrus.org/fpga_atlys_design/ 上にあります.

2015,10,7

ssatoh@

足立工科大学 工学部 情報通信工学科